L’evoluzione dei sistemi elettronici ha imposto requisiti sempre più stringenti in termini di velocità di commutazione, densità di componenti e affidabilità operativa. Quando i segnali digitali superano la soglia dei 100 MHz, o quando i tempi di salita scendono sotto i 5 nanosecondi, le prestazioni non dipendono più solo dalla qualità dei componenti, ma dalla fisica stessa del circuito stampato.

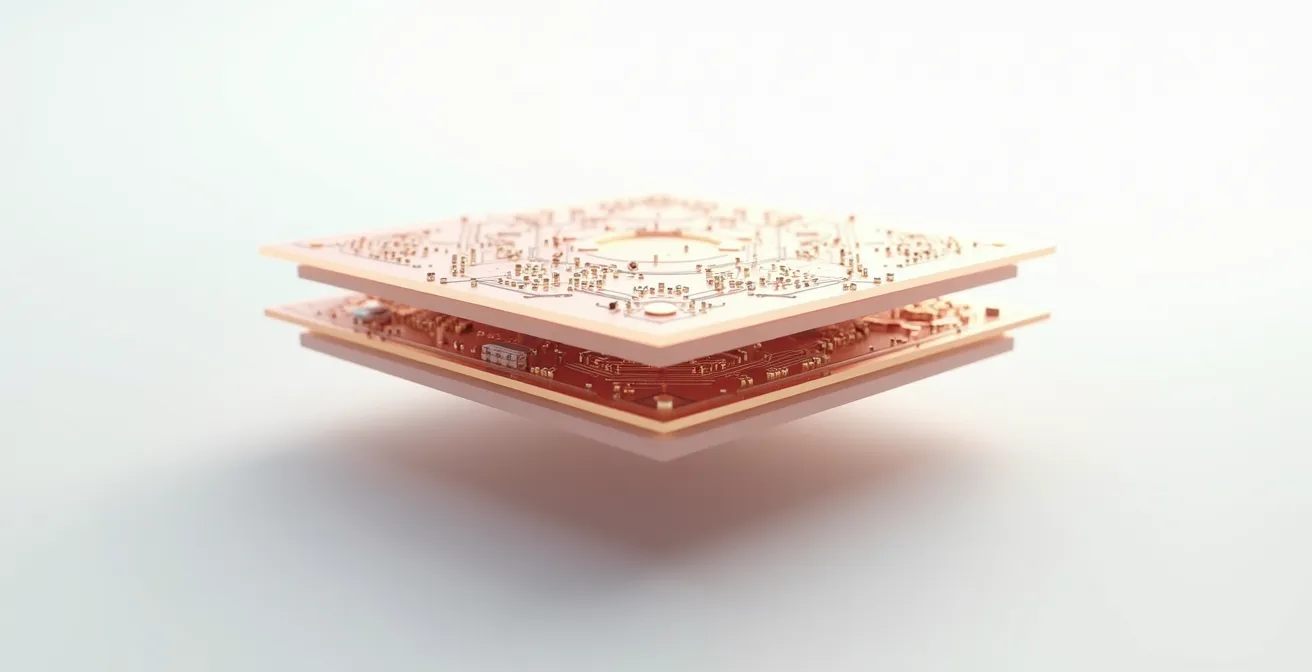

In questo contesto, i multilayer PCB rappresentano una risposta progettuale che va oltre la semplice necessità di compattare lo spazio. La stratificazione introduce meccanismi di controllo elettromagnetico che non esistono nelle architetture a doppia faccia, trasformando la struttura stessa del PCB in un elemento attivo nella gestione del segnale.

Questo articolo esplora i meccanismi fisici sottostanti che determinano il miglioramento delle prestazioni, trasformandoli in criteri concreti di progettazione. Dalla riduzione dell’impedenza parassita al dimensionamento termico, ogni aspetto verrà analizzato con un approccio quantitativo che permette di giustificare tecnicamente ed economicamente la complessità aggiuntiva.

Prestazioni PCB multistrato: i vantaggi tecnici essenziali

- La stratificazione riduce l’impedenza parassita nei percorsi critici attraverso piani di riferimento ravvicinati

- Piani di massa e alimentazione dedicati confinano i campi elettromagnetici riducendo EMI e crosstalk

- La gestione termica integrata migliora simultaneamente distribuzione di potenza e dissipazione del calore

- Criteri quantitativi permettono di determinare quando la complessità aggiuntiva è giustificata

Come la stratificazione riduce l’impedenza parassita nei percorsi critici

Il comportamento dinamico di un segnale digitale non dipende solo dalla resistenza della traccia conduttiva, ma dall’impedenza totale del percorso, che include componenti induttive e capacitive parassite. Queste impedenze non desiderate si manifestano particolarmente quando la frequenza aumenta o quando i tempi di transizione si riducono.

La chiave per comprendere il vantaggio dei PCB multistrato risiede nella relazione geometrica tra traccia conduttiva e piano di riferimento. Quando una corrente attraversa una traccia, genera un campo magnetico che si concatena con il percorso di ritorno. Più questo percorso è distante, maggiore è l’area del loop magnetico e quindi l’induttanza parassita. Nei PCB a doppia faccia, il percorso di ritorno può trovarsi a millimetri di distanza, creando loop di diverse decine di millimetri quadrati.

I dati sperimentali confermano l’impatto quantificabile di questa geometria. Analisi recenti dimostrano che configurazioni ottimizzate possono raggiungere valori di 31.28ps di ritardo con capacità parassita di 0.517pF, prestazioni irraggiungibili in strutture convenzionali a due strati.

| Parametro | Valore tipico | Impatto sul segnale |

|---|---|---|

| Induttanza parassita via | 1.015 nH | Impedenza 3.19Ω a 1ns rise time |

| Capacità parassita | 0.31-0.517 pF | Ritardo 2-31ps |

| Riduzione con piani dedicati | -65% | Miglioramento rise time |

Nei PCB multistrato, l’inserimento di piani di riferimento dedicati a distanze di 0.1-0.2 mm dalla traccia di segnale riduce drasticamente l’area del loop. La corrente di ritorno scorre direttamente sotto la traccia attiva, nel piano di rame più vicino, creando un accoppiamento capacitivo controllato che stabilizza l’impedenza caratteristica lungo tutto il percorso.

L’ESR così basso che lo zero dell’ESR viene spinto a una frequenza molto alta, il che significa che il suo boost di fase stabilizzante viene perso

– Ingegneri Magellan Circuits, Magellan Circuits Technical Documentation

Questa configurazione diventa critica quando si lavora con segnali veloci. Un tempo di salita di 1 nanosecondo corrisponde a componenti armoniche significative fino a 350 MHz. A queste frequenze, un’induttanza parassita di soli 1 nH genera un’impedenza di circa 3.2 Ω, sufficiente a degradare l’integrità del segnale e introdurre ringing significativo.

Il controllo dell’impedenza parassita attraverso la stratificazione consente di mantenere tracce con geometrie controllate. In un PCB a quattro strati, una configurazione tipica prevede segnali esterni con piani di riferimento immediatamente sottostanti, separati da un dielettrico di spessore standardizzato che permette di calcolare con precisione l’impedenza caratteristica della linea di trasmissione.

La riduzione dell’impedenza parassita si traduce in benefici misurabili sulla qualità del segnale. Il ringing post-transizione diminuisce, il tempo di stabilizzazione si accorcia e i margini di rumore migliorano. Questi vantaggi diventano determinanti in applicazioni ad alta velocità dove ogni picosecondo di jitter può compromettere la sincronizzazione o dove margini di tensione ridotti richiedono segnali puliti per garantire corrette letture logiche.

La progettazione ottimale richiede un approccio sistemico. Non basta inserire piani di riferimento: occorre garantire continuità lungo tutto il percorso del segnale, evitare gap nei piani sotto tracce critiche e dimensionare correttamente i via di transizione tra strati. Ogni discontinuità rappresenta una variazione di impedenza che può generare riflessioni e degradare le prestazioni complessive del sistema.

Controllo del campo elettromagnetico attraverso piani di alimentazione dedicati

Oltre alla riduzione dell’impedenza parassita, la stratificazione introduce un secondo meccanismo fisico di miglioramento: il confinamento dei campi elettromagnetici. Quando una corrente alternata attraversa una traccia, genera simultaneamente un campo elettrico (dovuto alla variazione di tensione) e un campo magnetico (dovuto alla corrente stessa). Senza un controllo adeguato, questi campi si propagano nello spazio circostante, accoppiandosi con altre tracce e generando interferenze.

I piani di massa e alimentazione dedicati agiscono come schermi elettromagnetici dinamici. Il campo elettrico generato da una traccia di segnale termina naturalmente sul piano di riferimento più vicino, creando un accoppiamento capacitivo distribuito. Il campo magnetico, invece, induce correnti di ritorno che scorrono nel piano immediatamente sottostante, seguendo il percorso di minima impedenza direttamente sotto la traccia attiva.

Analisi EMC in PCB multistrato per automotive

Studio del 2024 mostra come l’implementazione di piani di massa dedicati in PCB automotive riduce le emissioni elettromagnetiche del 20dB rispetto a design a 2 strati. La segmentazione corretta dei piani e l’uso di ponti di terra ha eliminato problemi di crosstalk in applicazioni critiche.

Questo meccanismo di confinamento diventa particolarmente efficace quando la distanza tra piano di segnale e piano di riferimento è molto inferiore alla distanza tra tracce adiacenti. In una configurazione tipica a quattro strati, con segnali esterni e piani interni separati da 0.2 mm di dielettrico, il campo elettromagnetico viene confinato in uno spazio tridimensionale ristretto, riducendo drasticamente l’accoppiamento capacitivo e induttivo tra tracce vicine.

La distanza critica per un confinamento efficace dipende dalla geometria specifica, ma generalmente quando il rapporto tra distanza traccia-piano e distanza tra tracce scende sotto 0.5, il crosstalk si riduce di oltre 15 dB. Configurazioni a quattro strati possono raggiungere riduzioni di 20-25 dB rispetto a PCB a doppia faccia, come dimostrato in applicazioni automotive critiche dove le specifiche EMC sono particolarmente stringenti.

Un aspetto spesso trascurato riguarda il percorso di ritorno della corrente ad alta frequenza. Alle basse frequenze, la corrente segue il percorso di minima resistenza. Alle alte frequenze, domina invece il percorso di minima impedenza, che coincide con quello di minima induttanza. In un PCB multistrato, questo percorso è direttamente sotto la traccia di segnale, nel piano di riferimento più vicino, creando un loop di area minima.

Quando un segnale attraversa diversi strati, i via di transizione diventano punti critici. Se il segnale passa da uno strato con un piano di massa come riferimento a uno strato con un piano di alimentazione come riferimento, la corrente di ritorno deve trovare un percorso capacitivo tra i due piani. Senza condensatori di disaccoppiamento posizionati strategicamente vicino al via, si crea una discontinuità del percorso di ritorno che genera emissioni elettromagnetiche e degrada l’integrità del segnale.

Il confronto quantitativo tra architetture diverse evidenzia i vantaggi. Un PCB a due strati tipicamente mostra emissioni radiate nell’ordine di 40-45 dBµV/m a 100 MHz per tracce di segnale veloci. La stessa configurazione in un quattro strati con piani dedicati può ridurre le emissioni a 20-25 dBµV/m, una riduzione di oltre 20 dB che spesso fa la differenza tra superare o fallire i test di compatibilità elettromagnetica.

L’integrazione di le tecnologie emergenti nell’elettronica richiede sempre più frequentemente architetture PCB capaci di gestire segnali misti, alta velocità e basso rumore simultaneamente. I piani dedicati permettono di segmentare funzionalmente il PCB, separando sezioni analogiche da digitali, o isolando circuiti di potenza da logica sensibile, mantenendo al contempo riferimenti comuni controllati.

Dimensionare gli strati in base ai requisiti di integrità del segnale

La scelta del numero di strati non dovrebbe derivare da convenzioni o da semplici considerazioni di densità di routing, ma da un’analisi sistematica dei requisiti di integrità del segnale. Il punto di partenza è il tempo di salita del segnale più veloce presente nel sistema, che determina la lunghezza critica oltre la quale le tracce devono essere trattate come linee di trasmissione.

La relazione fondamentale è semplice: una traccia diventa elettricamente lunga quando la sua lunghezza fisica supera un decimo della lunghezza d’onda corrispondente alla frequenza di ginocchio del segnale. Per un segnale con tempo di salita di 1 ns, la frequenza di ginocchio è circa 350 MHz, con lunghezza d’onda di circa 850 mm in FR4. La lunghezza critica risulta quindi di circa 85 mm, oltre la quale diventa necessario controllare rigorosamente l’impedenza caratteristica.

Quando le tracce superano questa lunghezza critica, la presenza di un piano di riferimento continuo e ravvicinato diventa essenziale. Senza piano di riferimento, l’impedenza caratteristica varia in modo incontrollato lungo il percorso, generando riflessioni multiple che degradano il segnale. In un PCB a due strati, è praticamente impossibile garantire impedenza controllata su tracce lunghe, rendendo inevitabile il passaggio a configurazioni multistrato.

Una metodologia pratica per determinare la configurazione ottimale parte dall’inventario dei segnali critici. Si classificano prima i segnali per velocità: quelli con tempo di salita inferiore a 2 ns richiedono impedenza controllata rigorosa. Si identificano poi le lunghezze delle tracce: percorsi superiori a 50 mm per segnali sub-nanosecondo necessitano certamente di piani di riferimento dedicati.

La densità di routing costituisce il secondo fattore determinante. Se il numero di connessioni richieste supera la capacità di routing di due strati mantenendo larghezze di traccia compatibili con l’impedenza target, la stratificazione diventa obbligatoria. Una regola empirica: quando più del 60% della superficie del PCB è occupata da tracce di segnale, è il momento di considerare strati aggiuntivi per evitare compromessi sulla geometria.

La matrice decisionale combina questi fattori in modo sistematico. Per frequenze fino a 50 MHz e densità bassa, due strati possono essere sufficienti. Tra 50 e 200 MHz con densità media, quattro strati diventano la scelta standard. Oltre 500 MHz o con requisiti di impedenza differenziale controllata, sei o più strati sono spesso necessari per mantenere l’integrità del segnale e garantire routing completo senza compromessi.

Un aspetto critico spesso sottovalutato riguarda le coppie differenziali. Segnali come USB, HDMI, Ethernet o PCIe richiedono non solo impedenza controllata, ma anche perfetto bilanciamento tra le due linee della coppia. Questo richiede routing accoppiato su uno stesso strato, con piano di riferimento continuo sottostante. In un due strati, garantire queste condizioni per più coppie differenziali diventa rapidamente impossibile.

La metodologia di dimensionamento deve inoltre considerare l’evoluzione futura del progetto. Un PCB progettato al limite delle capacità di un due strati non lascia margine per modifiche o aggiunte successive. L’investimento iniziale in un quattro strati può rivelarsi economicamente vantaggioso se permette revisioni senza riprogettazione completa dell’architettura.

Gestione termica accoppiata alla distribuzione della potenza

I piani di rame interni nei PCB multistrato svolgono una funzione duale spesso sottovalutata: oltre a servire come riferimenti elettrici per il controllo dell’impedenza e il confinamento dei campi elettromagnetici, agiscono simultaneamente come dissipatori termici distribuiti. Questa sinergia tra funzione elettrica e termica rappresenta uno dei vantaggi meno evidenti ma più significativi della stratificazione.

La resistenza termica di un PCB dipende fortemente dalla quantità e dalla distribuzione del rame negli strati interni. Un piano di rame da 35 µm di spessore offre già una capacità termica significativa, ma quando si passa a 70 µm o a configurazioni heavy copper da 105-400 µm, la capacità di assorbire e distribuire il calore aumenta proporzionalmente. Questa massa termica aggiuntiva riduce i picchi di temperatura localizzati e migliora l’uniformità termica del sistema.

Il calcolo della resistenza termica deve considerare non solo lo spessore del rame, ma anche la configurazione degli strati. Un quattro strati con due piani interni di rame offre percorsi di conduzione termica molto più efficaci rispetto a un due strati dove il calore deve propagarsi lateralmente attraverso tracce sottili. La presenza di via termici che connettono componenti caldi ai piani interni crea percorsi di fuga termica a bassa resistenza.

Esiste però un trade-off fondamentale tra prestazioni termiche ed elettriche. Aumentare lo spessore del rame dei piani migliora la dissipazione termica e riduce la resistenza DC per la distribuzione di potenza, ma aumenta simultaneamente la capacità parassita tra piano di alimentazione e piano di massa. Questa capacità aggiuntiva può essere vantaggiosa per il disaccoppiamento ad alta frequenza, ma complica il controllo dell’impedenza delle tracce di segnale.

L’impatto della temperatura sulle prestazioni elettriche crea un ciclo di retroazione che deve essere considerato in fase progettuale. La resistività del rame aumenta dello 0.4% per ogni grado Celsius. Un componente che dissipa potenza e aumenta la temperatura del piano di alimentazione locale di 30°C può vedere un aumento della resistenza DC del 12%, peggiorando la regolazione della tensione e aumentando ulteriormente la dissipazione per effetto Joule.

I tempi di propagazione dei segnali digitali sono anch’essi sensibili alla temperatura. La costante dielettrica del materiale FR4 varia con la temperatura, modificando la velocità di propagazione. In applicazioni critiche dove il timing è serrato, variazioni termiche di decine di gradi possono introdurre skew sufficiente a compromettere la sincronizzazione, specialmente in bus paralleli ad alta velocità.

La distribuzione della potenza beneficia direttamente dalla stratificazione. Piani di alimentazione dedicati offrono resistenza DC molto bassa tra sorgente di alimentazione e carichi distribuiti. Mentre in un due strati la distribuzione avviene attraverso tracce di larghezza limitata con resistenze dell’ordine di decine di milliohm, un piano di rame solido può ridurre questa resistenza di un ordine di grandezza, migliorando la regolazione e riducendo le perdite.

La strategia di via termici richiede pianificazione accurata. Il numero, il diametro e la disposizione dei via sotto componenti caldi determina l’efficacia della conduzione termica verso i piani interni. Una regola pratica suggerisce almeno un via per ogni mezzo watt dissipato, con spacing di 1-1.5 mm per creare un array termicamente efficace. Via di diametro maggiore migliorano la conduzione ma riducono lo spazio disponibile per il routing.

L’ottimizzazione finale richiede simulazione termica accoppiata con analisi elettrica. Strumenti moderni permettono di valutare simultaneamente distribuzione della temperatura, drop di tensione sui piani di alimentazione e impatto termico sui tempi di propagazione. Questo approccio integrato rivela compromessi non evidenti nell’analisi separata dei domini termico ed elettrico, permettendo scelte progettuali più informate e bilanciate.

Punti chiave

- La stratificazione riduce l’impedenza parassita fino al 65% attraverso piani di riferimento ravvicinati

- Confinamento elettromagnetico con piani dedicati abbatte le emissioni EMI di oltre 20 dB

- Il dimensionamento degli strati deve partire dai requisiti di integrità del segnale, non solo dalla densità

- Piani di rame interni svolgono funzione duale elettrica e termica con trade-off da bilanciare

- Criteri quantitativi di budget e margini permettono decisioni tecniche ed economiche oggettive

Criteri quantitativi per giustificare l’investimento in complessità

La decisione di adottare architetture PCB multistrato non può basarsi esclusivamente su considerazioni tecniche qualitative. Occorre un framework quantitativo che permetta di valutare oggettivamente quando la complessità aggiuntiva è giustificata dal miglioramento delle prestazioni e dall’impatto economico complessivo del progetto.

Il budget di integrità del segnale costituisce il primo criterio misurabile. Ogni segnale digitale ad alta velocità dispone di un margine di tensione tra livelli logici. Ad esempio, in logica LVCMOS 3.3V, il margine di rumore è tipicamente 400 mV. Ogni degradazione del segnale (ringing, crosstalk, drop resistivo, rumore di alimentazione) consuma parte di questo budget. Quando la somma delle degradazioni supera il 50% del margine disponibile, il sistema diventa vulnerabile e richiede architetture più robuste.

Un calcolo pratico per un segnale con tempo di salita di 1 ns su traccia da 100 mm in un due strati può mostrare: ringing da impedenza non controllata 200 mV, crosstalk da tracce adiacenti 150 mV, rumore di alimentazione 100 mV. Totale: 450 mV, che supera ampiamente il 50% del margine disponibile. La stessa configurazione in un quattro strati può ridurre ciascun contributo del 60-70%, riportando il sistema in condizioni sicure.

Il costo del re-design rappresenta il secondo fattore economico cruciale. Un PCB a due strati progettato al limite delle sue possibilità ha alta probabilità di richiedere modifiche quando emergono problemi di integrità del segnale o EMI durante i test. Il costo di una iterazione aggiuntiva (prototipazione, test, ritardo sul mercato) supera spesso di molto il differenziale di costo iniziale tra due e quattro strati. Un’analisi di rischio corretta deve considerare questa probabilità.

La metodologia di valutazione costo-beneficio parte dall’identificazione delle metriche elettriche critiche per l’applicazione specifica. Per un sistema di comunicazione, potrebbero essere bit error rate e jitter. Per un sistema di controllo, tempo di risposta e immunità al rumore. Per ogni metrica, si definisce un target minimo accettabile e si valuta quale architettura PCB permette di raggiungerlo con maggiore margine di sicurezza.

Le soglie di decisione possono essere formalizzate attraverso regole pratiche. Un due strati diventa insufficiente quando: frequenze di clock superano 100 MHz con fanout elevato, tempi di salita scendono sotto 2 ns, sono presenti più di due coppie differenziali ad alta velocità, o la densità di routing supera il 70% della superficie disponibile. Al contrario, sei strati diventano eccessivi quando le frequenze restano sotto 200 MHz, non ci sono requisiti di impedenza differenziale rigorosa, e la dissipazione termica totale è inferiore a 5W.

Un aspetto spesso trascurato riguarda la scalabilità della produzione. PCB complessi richiedono fornitori qualificati, processi più controllati e test più approfonditi. Questo può tradursi in lead time maggiori e minore flessibilità nella scelta dei fornitori. Per volumi bassi o prototipi, questo overhead può non essere giustificato. Per produzioni di serie, invece, l’investimento in processi stabili e qualificati ripaga ampiamente in termini di rese e affidabilità.

L’analisi deve anche considerare l’evoluzione tecnologica. Componenti elettronici diventano progressivamente più veloci e compatti. Un progetto dimensionato al limite delle capacità di un due strati oggi potrebbe diventare impossibile da evolvere domani senza riprogettazione completa. Investire in un quattro strati offre margine per future evoluzioni, prolungando la vita del progetto e ammortizzando meglio i costi di sviluppo iniziali.

Per progetti industriali critici, Ottimizza i processi industriali significa anche adottare architetture PCB che minimizzano i rischi di rilavorazione e garantiscono margini operativi adeguati per variabilità di processo e invecchiamento dei componenti.

La decisione finale richiede un approccio olistico. Confrontare non solo il costo del PCB grezzo, ma il costo totale del sistema: sviluppo, prototipazione, test, certificazioni, rilavorazioni, affidabilità in campo. Spesso un investimento del 30-50% superiore nel PCB si traduce in una riduzione del 20-30% del costo totale del progetto, grazie a minori iterazioni, maggiore affidabilità e time-to-market ridotto. Questi sono i criteri che trasformano una scelta tecnica in una decisione di business informata e razionale.

Domande frequenti sui PCB multistrato

Qual è lo spessore ottimale del rame per dissipazione termica?

Per applicazioni standard 35-70μm sono sufficienti. Per potenze superiori a 5A per traccia, si consiglia 105μm o tecnologia heavy copper fino a 400μm.

Come calcolare il numero di via termici necessari?

Come regola generale: 1 via ogni 0.5W di potenza dissipata. Per calcoli precisi considerare resistenza termica target e utilizzare array di via con spacing 1-1.5mm.

Quando un segnale digitale richiede impedenza controllata?

Quando la lunghezza della traccia supera un decimo della lunghezza d’onda corrispondente al tempo di salita del segnale. Per tempi di salita sotto 2ns, tracce superiori a 50mm necessitano generalmente di controllo di impedenza.

Qual è il vantaggio principale dei piani di massa dedicati?

Forniscono un percorso di ritorno della corrente a bassa impedenza direttamente sotto le tracce di segnale, riducendo l’area del loop magnetico e confinando i campi elettromagnetici. Questo riduce crosstalk ed emissioni EMI tipicamente di 20dB o più rispetto a configurazioni a due strati.